I/O 接口

Q: IO 接口有哪些端口? (三个)

A: 数据端口, 状态端口和控制端口

Q: IO 端口的两种编址方式

A: - 独立编址:

对所有的 I/O 端口单独进行编址.

I/O 端口的地址空间与主存地址空间是两个独立的地址空间, 它们的范围可以重叠, 相同地址可能属于不同的地址空间.

需设置专门的 I/O 指令来表明访问的是/O 地址空间

- 统一编址:

是指把主存地址空间分出一部分给 I/O 端口进行编址

I/O 端口和主存单元在同一地址空间的不同分段中,

根据地址范围就能区分访问的是 I/O 端口还是主存单元

无须设置专门的 I/O 指令, 用统一的访存指令就可访问 I/O 端口

Q: 总线中的三条不同线的作用

数据线, 控制线, 地址线

A: 数据线: 读/写数据, I/O 接口中的命令字, 状态信息, 控制信息和中断类型号

控制线: 控制信号, 中断请求和响应信号, 仲裁信号和握手信号

地址线: 要访问 I/O 接口中的寄存器的地址

Q: 总线上传输状态信号与状态信息的线为?

A: 状态信号: 控制线

状态信息: 数据线

I/O 方式

Q: 主机访问 I/O 设备的三大控制方式

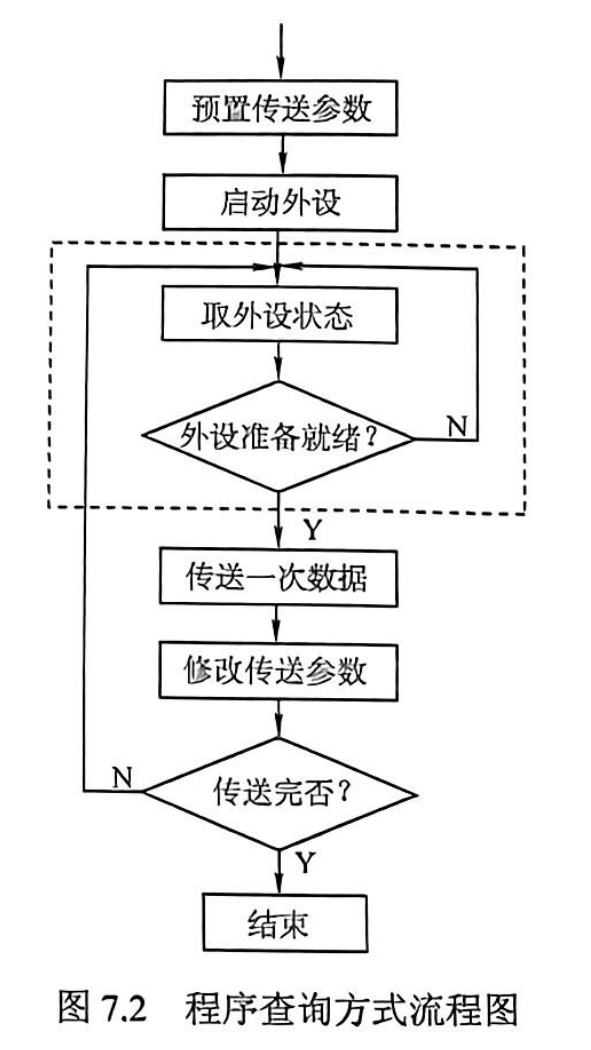

A: - 程序直接控制:

CPU 负责执行所有与 I/O 操作相关的指令和数据传输. CPU 会不断地轮询 I/O 设备的就绪状态, 直到设备准备好进行数据传输

- 中断驱动:

当 I/O 设备完成一个操作后, 会向 CPU 发出中断请求, 通知 CPU 进行相应的处理.

CPU 在执行完当前指令后, 会响应中断请求, 转到相应的中断服务程序处理 I/O 操作. - DMA:

DMA 是一种允许外设直接访问主存的控制方式, 无需 CPU 的直接干预.

DMA 控制器负责管理 I/O 数据传输, CPU 只需在传输开始和结束时进行设置和通知.

Q: 主机访问 I/O 设备的三大控制方式, 效率区别

程序直接控制, 中断驱动, DMA

A: 程序直接控制, 效率最低

中断驱动, 效率居中

DMA, 效率最高

哪些外设适合使用中断驱动方式进行 I/O?

{键盘}

{鼠标}

{打字机}

{定时器/时钟}

字符型设备

哪些外设适合使用DMA方式进行 I/O?

{磁盘}

{网卡}

{显卡}

{声卡}

{数据采集卡}

程序直接驱动

独占查询

CPU 一直持续查询外设接口, 获取设备状态

定时查询

周期性查询外设接口, 获取设备状态

中断驱动

Q: 开中断情况下, CPU 检测到中断就一定会立即响应吗?

A: 是的

在开中断情况下, CPU 在条指令执行结束时检测到中断请求信号, 则会立即响应

即便是多重中断, CPU 正在处理某个中断的过程中, 由于中断屏蔽字的存在, CPU 检测不到处理优先级更低的中断请求信号, 因此若检测到中断请求信号, 则说明新中断源的处理优先级更高, 同样也会立即响应

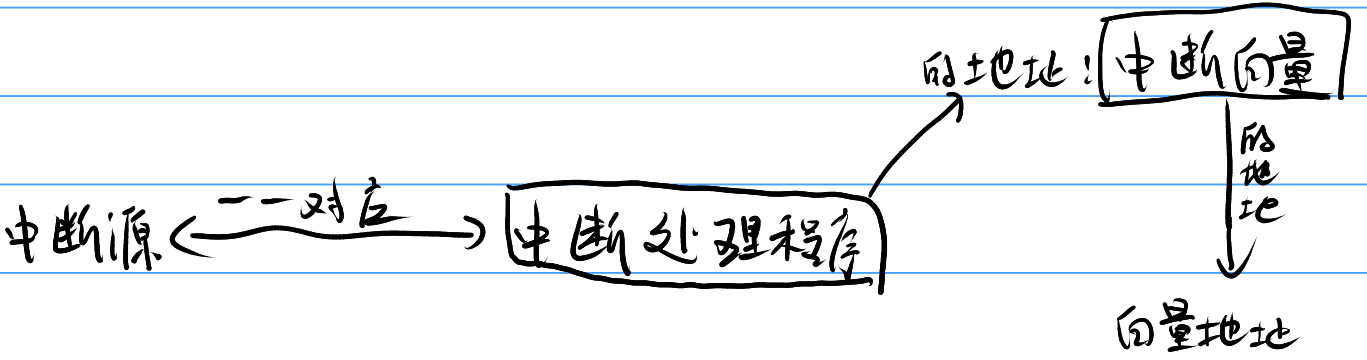

Q: 中断源, 中断处理程序, 中断向量, 向量地址的关系

A: 中断源发出中断请求信号

系统收到中断请求信号后, 进入中断向量表查

根据中断编号在中断向量表中得到中断处理程序地址

根据中断处理程序地址, 运行中断处理程序

Q: 中断隐指令执行的三步操作

A: 关中断

保存断点: 保存 PC 和 PSW

引出中断服务程序

Q: 中断隐指令由软件执行还是由硬件执行?

A: 由硬件自动完成的一系列微操作.

Q: 为什么中断隐指令由硬件完成, 但被叫作隐指令?

Q: 由硬件完成的, 对程序员是透明的, 且其功能类似一条复杂的指令, 所以被称为”隐指令”.

Q: 可屏蔽中断, 内部异常, 不可屏蔽中断优先级排序, 从低到高

A: 可屏蔽中断<内部异常<不可屏蔽中断

Q: CPU 处于中断屏蔽状态下会响应哪些中断请求?

A: 不可屏蔽中断

内部异常

DMA

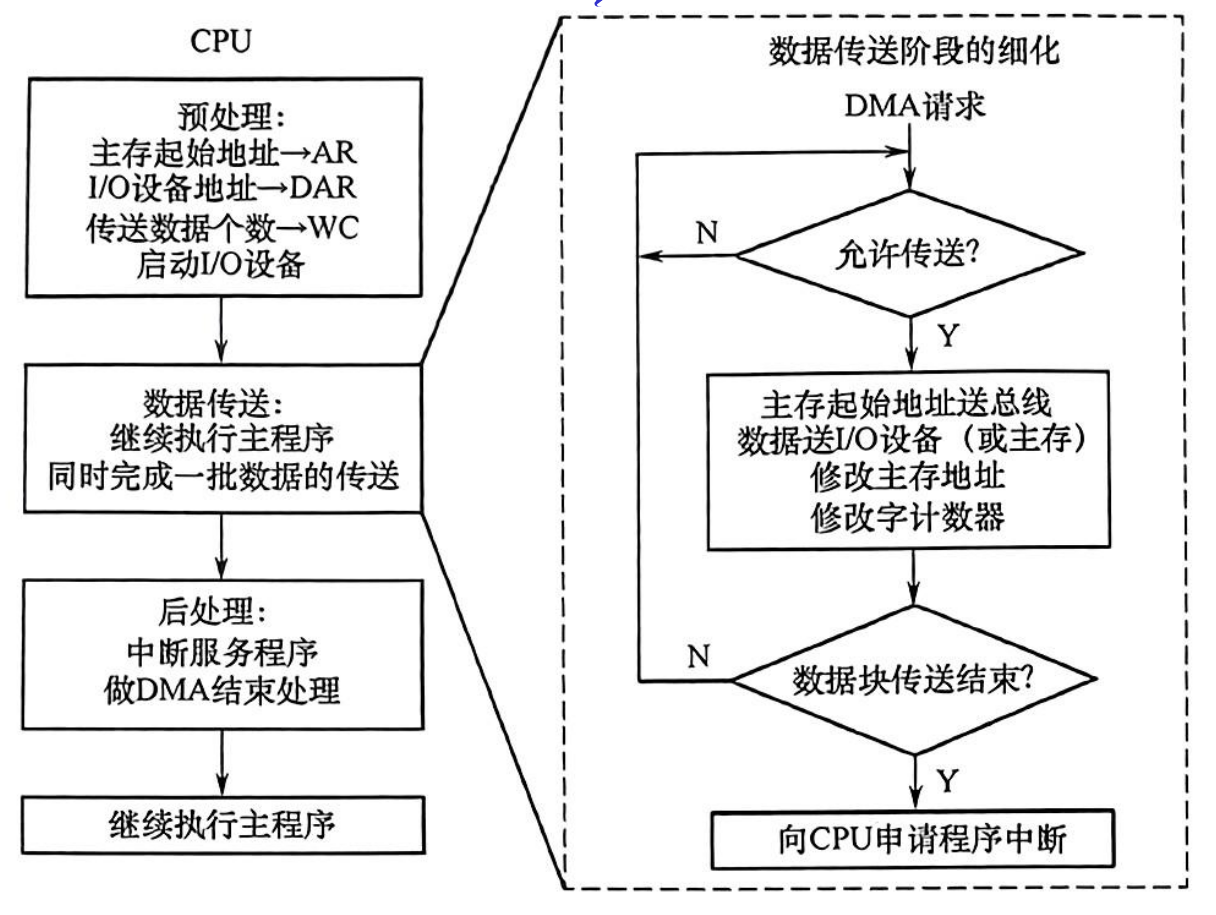

主机访问 I/O 设备, DMA 方式

主存和 DMA 接口之间有一条直接数据通路

DMA 方式传送数据不需要经过 CPU

DMA 方式传送 IO 设备数据过程

预处理, 传输, 后处理

IO 设备 DMA 方式和中断方式, 传输阶段的重要区别

- 无需中断: DMA 不需要中断, 也不需要保护现场, 只有预处理和后处理占用 CPU 资源

- 任意响应: CPU 对 DMA 请求的相应可以在任意一个机器周期结束时 (取指, 间址, 执行周期后均可)

- 传输效率高: 直接硬件执行, 不需要 CPU, 传输效率高

Q: DMA 请求与 (普通) 中断请求谁优先级更高?

A: DMA 请求的优先级高于中断请求

掉电中断请求高于 DMA 请求

使用 DMA 方式进行 I/O, 有以下三种传送方式

{CPU 停止法}/{成组传送}

{周期挪用法}/{单字传送}

{交替分时访问法}/{透明传送}

在 DMA 的 CPU 停止法 (成组传送) 模式下, DMA 传输时, CPU{脱离总线, 停止访问主存}, 直到 DMA 传送完一整块数据.

Q: DMA 的哪种传送方式会使 CPU 在整个数据块传输期间完全暂停工作?

A: CPU 停止法 (成组传送 / Burst Mode)

Q: 在 DMA 的周期挪用模式中, 当 I/O 和 CPU 同时请求访存时, 谁的优先级更高? 为什么?

A: I/O 访存优先级更高.

Q: 为什么在 DMA 的周期挪用模式中, 当 I/O 和 CPU 同时请求访存时, I/O 访存优先级更高?

A: 因为 I/O 设备若不立即访存, 就可能丢失数据.

DMA 的周期挪用模式, 是在 I/O 需要时 “挪用” 一个或几个存取周期, 传送完一个 {总线字} 后立即释放总线, 因此也称为 {单字传送} 方式.

Q: 在 DMA 的周期挪用模式下, 如果 CPU 正在访存, I/O 设备可以立即抢占总线吗?

A: 不可以. 必须等待 CPU 当前的存取周期结束后, CPU 才会让出总线占有权.

DMA 的交替分时访问模式, 其原理是将 CPU 周期分为两部分, 一部分专供 {DMA 访存}, 另一部分专供 {CPU 访存}.

Q: CPU 周期与存储周期什么情况下适合使用交替分时访问 (透明传送)?

A: CPU 周期长而存储周期短

Q: 为什么 “交替分时访问” 模式又被称为 “透明传送”?

A: 因为 DMA 访存利用的是 CPU 不访存的空闲时间, 对 CPU 来说是透明的 (感觉不到 DMA 的存在), CPU 无需中断或等待, 运行效率不会下降.

Q: DMA 的哪种传送方式不需要申请、建立和归还总线的使用权?

A: 交替分时访问 (透明传送) 模式.