存储器概述

Q: 现代的 ROM 存储器可以实现随机存取操作吗?

A: 可以

最开始的 ROM 只支持读出, 而不支持写入

现代的 ROM, 保留了非易失性, 随机读出的特点, 也支持了随机写入操作

Q: 什么是 CDROM?

A: 光盘

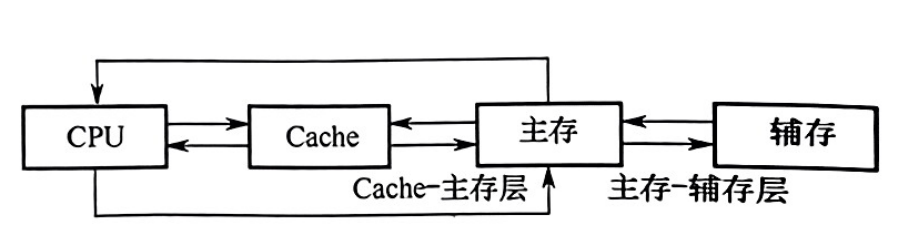

Q: CPU, Cache, 主存, 外存之间的通信情况, 画图

A:

Q: CPU 可以与外存直接交换信息吗?

A: 不可以

外存只能与主存之间交换

Q: Cache 与主存之间, 主存与外存之间的关系 (副本)

A: Cache 是主存的部分内容的副本

主存是外存的部分内容的副本

主存储器 DRAM 与 SRAM

主存储器由 {DRAM} 实现

Cache 则由 {SRAM} 实现

是否是破坏性读出

SRAM{非破坏性读出}

DRAM{破坏性读出}

Q: 为什么 SRAM 是非破坏性读出, DRAM 是破坏性读出 ?

A: 与它们的物理实现原理有关

SRAM 的存储元是用双稳态触发器 (六晶体管 MOS) 来记忆信息的, 静态是指即使信息被读出后, 它仍保持其原状态而不需要再生 (非破坏性读出).

DRAM 是利用存储元电路中栅极电容上的电荷来存储信息的, 电容上的电荷一般只能维持 1~2ms, 因此即使电源不断电, 信息也会自动消失. 此外, 读操作会使其状态发生改变, 所以必须定时刷新和读后再生

Q: 什么是 DRAM 的刷新周期

A: 对同一行进行相邻两次刷新的时间间隔称为刷新周期

Q: DRAM 的三大刷新策略

A: 集中刷新: 在一个刷新周期内, 对所有的 DRAM 行进行统一刷新

分散刷新: 系统的读写周期=2*芯片读写周期. 例如原来的芯片读写周期为 0.5us, 使用分散刷新之后, 芯片的读写周期没有变化, 但是系统的读写周期变为 1.0us. 在一个系统读写周期中, 一半用于读写, 一半用于刷新

异步刷新: T=最大刷新间隔/行数. 每 T 时间内刷新一行. 一个最大刷新间隔内, 所有行都被刷新过

DRAM 不同刷新策略有无死区

集中刷新: {c1: 有死区}

分散刷新: {c1: 无死区}

异步刷新: {c1: 有死区}

Q: DRAM 集中刷新与异步刷新, 死区的区别 (连续性)

A: 集中刷新, 死区连续

异步刷新, 死区分散

从维度看 SRAM 与 DRAM

SRAM 是一维的

DRAM 是二维的

Q: DRAM 为什么是二维的?

A: 与 DRAM 的物理结构有关

Q: DRAM 为什么是按照行来刷新, 按某个再生?

A: 似乎与物理结构有关

刷新只能整行刷新

复苏能够单个复苏

Q: 为什么 DRAM 采用地址引脚复用技术, SRAM 不使用?

A: SRAM 是一维, 而且 SRAM 对速度要求极高, 比较小, 地址线数量足够, 不需要使用地址引脚复用的技术

DRAM 是二维的, 对速度要求没有 SRAM 这么高, DRAM 比较大, 地址线数量可能不太够用

Q: DRAM 芯片行, 列数的优化原则

两条原则

A: |r-c|尽可能小

在此基础上

R⇐C

Q: 为什么 DRAM 芯片行, 列数的优化原则中

|r-c|尽可能小? 在此基础上 r⇐c?

A: |r-c|: 使用地址复用技术, 用较少的地址线, 能够映射较大的 DRAM

R⇐c: DRAM 需要进行刷新, 而刷新是按行为单位, r⇐c 可以减少刷新开销

多模块存储器

单体多字存储器

存储器存储单元大小={数据总线宽度}

Q: 高位交叉编址与低位交叉编址

体号与体内地址, 谁是高位, 谁是低位?

A: 高位交叉编址: 高位体号, 低位体内地址

低位交叉编址: 高位体内地址, 低位体号

Q: 高位交叉编址是串行还是并行?

A: 串行

由于体内地址在低位, 地址增加, 一般情况下, 高位体号不变, 一直在读取同一模块

Q: 低位位交叉编址是串行还是并行?

A: 并行

体号在低位, 地址增加, 体号变化, 读取的模块变化, 多个模块之间并行工作

交叉存储器的轮流启动方式

若每个模块一次读/写的位数正好等于数据总线位数, 模块的存取周期为 T, 总线周期为 r,

为实现轮流启动方式, 存储器交叉模块数应大于或等于{T/r}

Q: 存储器, 存取周期的定义

A: 两次独立访问存储器操作之间的最小间隔

一次存储周期中有存取时间与恢复时间

总线周期

CPU 通过系统总线与{c1:内存}或 {c1:I/O 设备}进行一次完整数据交换所需要的时间

通常由几个时钟周期组成

{机器}周期={总线}周期

Q: RAM 与 ROM 可以统一编址吗?

A: 可以, 例如

计算机的 BIOS 等固件通常放置在 ROM 中, 而系统的操作数据放在 RAM 中

两者都位于同一地址空间的不同区域中

Q: 采取随机存储方式进行随机访问的存储器一定是随机存储器吗?

A: 不一定

例如 RAM 与 ROM 都采取随机存储方式进行随机访问

但 ROM 并不是随机存储器, 而 RAM 有断点易失的特点, 为随机存储器

主存储器与 CPU 的连接

外部存储器

磁头数 (Heads): 表示磁盘中有多少{记录面}

柱面数 (Cylinders): 表示磁盘每面盘片上有多少{磁道}

扇区数 (Sectors): 表示每条磁道上有多少{扇区}

Q: 记录面, 磁道, 扇区的层次结构

A: 记录面上有磁道, 磁道上有扇区

Q: 磁盘格式化与非格式化的容量, 哪一个更大?

A: 非格式化

格式化之后, 相邻扇区间通过一定的间隙分隔开, 以避免精度错误, 导致容量变小

Q: 磁盘最小的读写单位是?

A: 扇区

Q: 磁盘寻址的过程

A: 先找到对应的磁道

在该磁道中找到对应的扇区

磁盘存取的时间组成 (三大部分)

{寻道时间}+{旋转延迟时间}+{数据传输时间}

磁盘转速为

经过一圈的时间

旋转延迟时间={

数据传输时间={

平均寻道时间:{从最外道移动到最内道时间的一半}

平均旋转延迟时间:{旋转半周的时间}

条带化技术

把连续多个数据块交替地存放在不同物理磁盘的扇区中,几个磁盘交叉并行读/写,

即条带化技术

高速缓冲存储器 Cache

Q: 局部性原理的定义

时间局部性

空间局部性

A: 时间局部性: 最近的未来需要用到的信息, 很可能是现在正在使用的信息

空间局部性: 最近的未来需要用到的信息, 在存储空间上, 很可能与现在正在使用的信息邻近

Q: Cache 和主存的三大映射方式

A: 直接映射

全相联映射

组相联映射

不同映射对于 CPU 传入的主存地址的不同解释

直接映射 {c1: tag (主存地址的高位)|Cache 行号 (主存地址的低位)|块内地址}

全相联映射{c1: tag (主存地址的高位)|块内地址}

组相联映射{c1: tag (主存地址的高位)|组号 (主存地址的低位)|块内地址}

| 直接映射 | 全相联映射 | 组相联映射 | |

|---|---|---|---|

| 比较器个数 | {c1:1} | {c1: cache 行数} | {c1: 组路数} |

| 比较器位数 | {c1: tag} | {c1: tag} | {c1: tag} |

Cache 与主存的一致性问题

- Cache 命中

- 全写:{同时更新 Cache 与主存}

- 回写:{先更新 Cache, 脏位置 1, 等待时机更新主存}

- Cache 未命中

- 写分配:{更新主存, 再把主存调入 Cache}

- 非写分配:{更新主存, 不调入 Cache}

Q: Cache 行对应一个标记项包括

A: 有效位, 脏位, 替换算法位, tag 位

虚拟存储器

Q: 为什么虚拟存储器只能采用回写法?

A: 虚拟存储器的存储机制: 主存中的页 (或段) 是外存的副本

修改虚拟存储器的内容, 直接修改主存中的副本, 再在合适的时候, 写回外存, 速度更快

如果采用全写法, 一起更新主存与外存的内容, 外存的时间开销过大

主存空间中的页称为物理页, 实页, 页框

虚拟地址空间中的页称为虚拟页, 虚页

Q: 页表项对应的 (一个标记项包括) 存储的元素

A: 有效位, 脏位, 替换算法位, 物理块号

Q: 若操作系统采用虚拟存储器(不含TLB),

一个逻辑地址被MMU分为哪两部分?

A: 高位: 页号

低位: 页内地址

Q: 若操作系统采用虚拟存储器(不含TLB),

一个物理地址被MMU分为哪两部分?

A: 高位: 页框号

低位: 页内地址

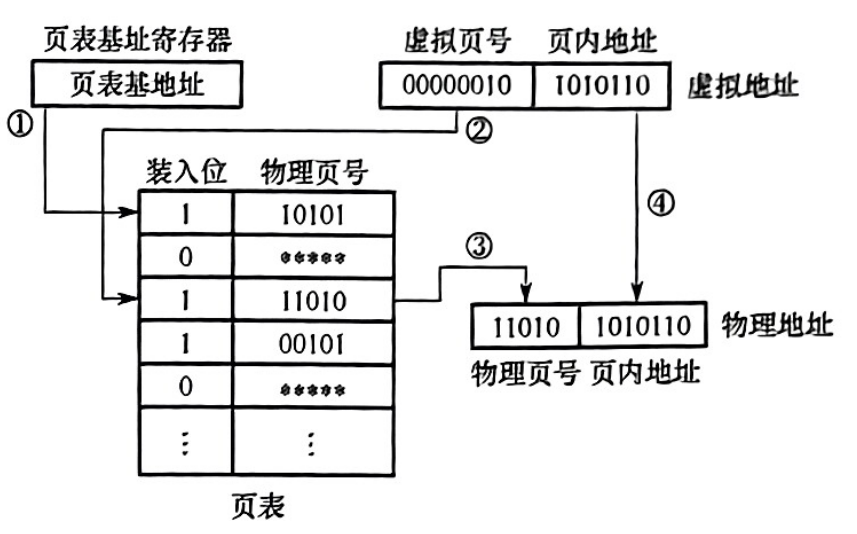

Q: 分页结构的逻辑地址到物理地址的转换过程

A: 根据逻辑地址高位的虚拟页号, 查找页表

在页表中找到对应的物理页号

将物理页号与逻辑地址低位的页内偏移合并, 成为物理地址

Q: 有TLB与没有TLB情况下,MMU对于传入的逻辑地址的解释

有什么不同?

A: 无TLB: 页号|页内地址

有TLB: tag|TLB行号/组号|页内地址

不同映射对于 CPU 传入的虚拟地址的不同解释

直接映射:{c1: tag (虚拟页号高位)|TLB 页号 (虚拟页号低位)|页内地址}

全相联映射:{c1: tag (虚拟页号)|页内地址}

组相连映射:{c1: tag (虚拟页号的高位)|TLB 组号 (虚拟页号的低位)|页内地址}

Q: 快表与慢表放置位置的区别

A: 快表: 高速缓冲器组成的快表 (TLB) 中

慢表: 主存中

虚拟地址映射到 TLB 与主存地址映射到 Cache 相同

Q: 页表如果没命中, 则 TLB 与 Cache 可能命中吗?

A: 不可能命中

TLB 与 Cache 说到底也就是主存部分的副本,

那么 TLB 与 Cache 根本不可能命中

页式虚拟存储器

优点是, 页面的长度固定, 页表简单, 调入方便

缺点是, 因为程序不可能正好是页面的整数倍, 最后一页的零头将无法利用而造成浪费, 并且页不是逻辑上独立的实体, 所以处理, 保护和共享都不及段式虚拟存储器方便.

段式虚拟存储器

优点是, 段的分界与程序的自然分界相对应, 因而具有逻辑独立性, 使得它易于编译, 管理, 修改和保护, 也便于多道程序的共享

缺点是, 因为段长度可变, 分配空间不便, 容易在段间留下碎片, 不好利用, 造成浪费.

段页式虚拟存储器

优点是, 兼具页式和段式虚拟存储器的优点, 可以按段实现共享和保护.

缺点是, 在地址变换过程中需要两次查表, 系统开销较大.

Cache 主要解决{系统速度}, 而虚拟存储器却是为了解决{主存容量}

Cache 全由硬件实现, 是硬件存储器, 对所有程序员透明; 而虚拟存储器由 OS 和硬件共

同实现, 是逻辑上的存储器,

Cache 缺失处理由硬件完成; 缺页处理由软件完成, 操作系统通过”缺页异常处理程序”

来实现; 而 TLB 缺失既可以用硬件, 又可以用软件来处理.